- 5 Seth uses a computer for work.

- (a) Complete the following descriptions of internal components of a computer by writing the missing terms.

| The                  | transmits the signals to coordinate events based on the                               |

|----------------------|---------------------------------------------------------------------------------------|

| electronic pulses of | the                                                                                   |

| The                  | carries data to the components, while the                                             |

|                      |                                                                                       |

|                      | carries the address where data needs to be written to or read                         |

| from.                |                                                                                       |

| The                  | performs mathematical operations and logical comparisons.                             |

|                      | [5]                                                                                   |

|                      |                                                                                       |

| (b) Describe the wa  | ays in which the following factors can affect the performance of his laptop computer. |

| Number of cores      |                                                                                       |

|                      |                                                                                       |

|                      |                                                                                       |

|                      |                                                                                       |

|                      |                                                                                       |

| Clock speed          |                                                                                       |

| \                    |                                                                                       |

|                      |                                                                                       |

|                      |                                                                                       |

|                      | [4]                                                                                   |

- 3 A processor has one general purpose register, the Accumulator (ACC), and several special purpose registers.

- (a) Complete the following description of the role of the registers in the fetch-execute cycle by writing the missing registers.

| The                         | holds the address of the next inst | ruction to be loaded |

|-----------------------------|------------------------------------|----------------------|

| This address is sent to the |                                    |                      |

| The                         | holds the data fetched from this   | s address. This data |

| is sent to the              | and the Control Unit d             | ecodes the           |

| instruction's opcode.       |                                    |                      |

| The                         | is incremented.                    | [5]                  |

**(b)** The following table shows part of the instruction set for a processor. The processor has one general purpose register, the Accumulator (ACC), and an Index Register (IX).

| Instruction Opcode Operand |                       | Explanation                                                                                                                                             |

|----------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |                       | Explanation                                                                                                                                             |

| LDM                        | #n                    | Immediate addressing. Load the number n to ACC                                                                                                          |

| LDD                        | <address></address>   | Direct addressing. Load the contents of the location at the given address to ACC                                                                        |

| LDI                        | <address></address>   | Indirect addressing: The address to be used is at the given address. Load the contents of this second address to ACC                                    |

| LDX                        | <address></address>   | Indexed addressing. Form the address from <address> + the contents of the Index Register. Copy the contents of this calculated address to ACC</address> |

| LDR                        | #n                    | Immediate addressing. Load the number n to IX                                                                                                           |

| MOV                        | <register></register> | Move the contents of the accumulator to the given register (IX)                                                                                         |

| STO                        | <address></address>   | Store contents of ACC at the given address                                                                                                              |

| ADD                        | <address></address>   | Add the contents of the given address to the ACC                                                                                                        |

| INC                        | <register></register> | Add 1 to the contents of the register (ACC or IX)                                                                                                       |

| CMP                        | <address></address>   | Compare the contents of ACC with the contents of <address></address>                                                                                    |

| JPE                        | <address></address>   | Following a compare instruction, jump to <address> if the compare was True</address>                                                                    |

| JPN                        | <address></address>   | Following a compare instruction, jump to <address> if the compare was False</address>                                                                   |

| JMP                        | <address></address>   | Jump to the given address                                                                                                                               |

| OUT                        |                       | Output to the screen the character whose ASCII value is stored in ACC                                                                                   |

| END                        | <b>Y</b>              | Return control to the operating system                                                                                                                  |

| LSL                        | #n                    | Bits in ACC are shifted logically n places to the left. Zeros are introduced on the right hand end                                                      |

| LSR                        | #n                    | Bits in ACC are shifted logically n places to the right. Zeros are introduced on the left hand end                                                      |

<address> can be an absolute address or a symbolic address # denotes a denary number, e.g. #123

The current contents of the main memory and selected values from the ASCII character set are shown.

| Address | Instruction |

|---------|-------------|

| 200     | LDD 365     |

| 201     | CMP 366     |

| 202     | JPE 209     |

| 203     | INC ACC     |

| 204     | STO 365     |

| 205     | MOV IX      |

| 206     | LDX 365     |

| 207     | OUT         |

| 208     | JMP 200     |

| 209     | END         |

|         | 7           |

| 365     | 1           |

| 366     | 3           |

| 367     | 65          |

| 368     | 66          |

| TX      | 0           |

### ASCII code table (selected codes only)

| ASCII code | Character |

|------------|-----------|

| 65         | A         |

| 66         | В         |

| 67         | С         |

| 68         | D         |

Complete the trace table for the program currently in main memory

| Instruction | 400   | Memory address |     |            |     | D/          |          |

|-------------|-------|----------------|-----|------------|-----|-------------|----------|

| address     | ACC   | 365            | 366 | 367        | 368 | IX          | Output   |

|             |       | 1              | 3   | 65         | 66  | 0           |          |

|             |       |                |     |            |     |             | <b>X</b> |

|             |       |                |     |            |     |             | <b>)</b> |

|             |       |                |     |            |     |             |          |

|             |       |                |     |            |     | 1.          |          |

|             |       |                |     |            |     | <b>&gt;</b> |          |

|             |       |                |     | ,          |     |             |          |

|             |       |                |     |            |     |             |          |

|             |       |                |     |            |     |             |          |

|             |       |                | 1   |            |     |             |          |

|             |       |                |     | <i>y y</i> |     |             |          |

|             |       |                | 45  | <b>1</b>   |     |             |          |

|             |       |                | 7 V |            |     |             |          |

|             |       |                |     |            |     |             |          |

|             |       |                |     |            |     |             |          |

|             | , , ( | 7              |     |            |     |             |          |

|             | •//   |                |     |            |     |             |          |

|             | 0.    |                |     |            |     |             |          |

| X           |       |                |     |            |     |             |          |

|             |       |                |     |            |     |             |          |

| 7           |       |                |     |            |     |             |          |

|             |       |                |     |            |     |             |          |

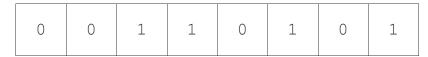

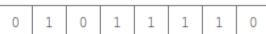

- (c) (i) The Accumulator currently contains the binary number:

- (c) (i) The Accumulator currently contains the binary number:

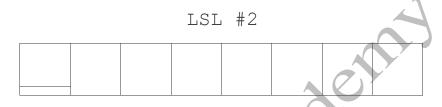

Write the contents of the Accumulator after the processor has executed the following instruction:

[1]

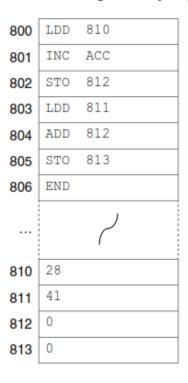

(ii) The Accumulator currently contains the binary number:

| 0 | 0 | 1        | 10 0 | 1 | 0 | 1 |

|---|---|----------|------|---|---|---|

|   |   | <b>(</b> |      |   |   |   |

Identify the mathematical operation that the following instruction will perform on the contents of the accumulator.

.....[1]

The table shows part of the instruction set for a processor. The processor has one general purpose register, the Accumulator (ACC), and an Index Register (IX).

| Instruction |                       | Fundametica                                                                           |

|-------------|-----------------------|---------------------------------------------------------------------------------------|

| Opcode      | Operand               | Explanation                                                                           |

| LDM         | #n                    | Immediate addressing. Load the number n to ACC                                        |

| LDD         | <address></address>   | Direct addressing. Load the contents of the location at the given address to ACC      |

| STO         | <address></address>   | Store contents of ACC at the given address                                            |

| ADD         | <address></address>   | Add the contents of the given address to the ACC                                      |

| INC         | <register></register> | Add 1 to the contents of the register (ACC or IX)                                     |

| DEC         | <register></register> | Subtract 1 from the contents of the register (ACC or IX)                              |

| CMP         | <address></address>   | Compare the contents of ACC with the contents of <address></address>                  |

| JPE         | <address></address>   | Following a compare instruction, jump to <address> if the compare was True</address>  |

| JPN         | <address></address>   | Following a compare instruction, jump to <address> if the compare was False</address> |

| JMP         | <address></address>   | Jump to the given address                                                             |

| IN          |                       | Key in a character and store its ASCII value in ACC                                   |

| OUT         |                       | Output to the screen the character whose ASCII value is stored in ACC                 |

| END         |                       | Return control to the operating system                                                |

# denotes a denary number, e.g. #123

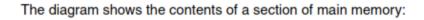

The current contents of the main memory and selected values from the ASCII character set are:

| Address | Instruction | ASCII code table |

|---------|-------------|------------------|

| 70      | IN          | ASCII code       |

| 71      | CMP 100     | 65               |

| 72      | JPE 80      | 66               |

| 73      | CMP 101     | 67               |

| 74      | JPE 76      | 68               |

| 75      | JMP 80      |                  |

| 76      | LDD 102     |                  |

| 77      | INC ACC     |                  |

| 78      | STO 102     |                  |

| 79      | JMP 70      |                  |

| 80      | LDD 102     |                  |

| 81      | DEC ACC     |                  |

| 82      | STO 102     |                  |

| 83      | JMP 70      |                  |

|         |             |                  |

| 100     | 68          |                  |

| 101     | 65          |                  |

|         | 100         |                  |

| <b>ASCII</b> | code | table | (selected | codes | only) |

|--------------|------|-------|-----------|-------|-------|

|--------------|------|-------|-----------|-------|-------|

| ASCII code | Character |

|------------|-----------|

| 65         | A         |

| 66         | В         |

| 67         | С         |

| 68         | D         |

(a) Complete the trace table for the program currently in main memory when the following characters are input:

A D

Do not trace the program any further when the third input is required.

| Instruction  | on ACC | N   | 3   |     |

|--------------|--------|-----|-----|-----|

| address      |        | 100 | 101 | 102 |

|              |        | 68  | 65  | 100 |

|              |        |     |     |     |

|              |        |     |     | 4.  |

|              |        |     | 5   |     |

|              |        |     |     |     |

|              |        |     | 120 |     |

|              |        |     |     |     |

|              |        |     |     |     |

|              |        |     | ,   |     |

|              |        |     |     |     |

|              |        | 170 |     |     |

|              |        |     |     |     |

|              | 00     |     |     |     |

|              |        |     |     |     |

|              |        |     |     |     |

| , (          |        |     |     |     |

| - 1          |        |     |     |     |

| • \ \        |        |     |     |     |

| <b>1</b> 00° |        |     |     |     |

|              |        |     |     |     |

|              |        |     |     |     |

|              |        |     |     |     |

|              |        |     |     |     |

|              |        |     |     |     |

|              |        |     |     |     |

|              |        |     |     |     |

**(b)** Some bit manipulation instructions are shown in the table:

| Instruction |                     | Evalenction                                                                           |

|-------------|---------------------|---------------------------------------------------------------------------------------|

| Opcode      | Operand             | Explanation                                                                           |

| AND         | #n                  | Bitwise AND operation of the contents of ACC with the operand                         |

| AND         | <address></address> | Bitwise AND operation of the contents of ACC with the contents of <address></address> |

| XOR         | #n                  | Bitwise XOR operation of the contents of ACC with the operand                         |

| XOR         | <address></address> | Bitwise XOR operation of the contents of ACC with the contents of <address></address> |

| OR          | #n                  | Bitwise OR operation of the contents of ACC with the operand                          |

| OR          | <address></address> | Bitwise OR operation of the contents of ACC with the contents of <address></address>  |

<address> can be an absolute address or a symbolic address # denotes a denary number, e.g. #123

| a denary number, e.g. #123 |       | •      |        |        |   | S | , ) |

|----------------------------|-------|--------|--------|--------|---|---|-----|

| The contents of the memory | addro | ess 30 | 00 are | shown: |   |   |     |

| Bit Number                 | 7     | 6      | 5      | 4 3    | 2 | 1 | 0   |

| 300                        | 0     | 1      | 1      | 0      | 1 | 1 | 0   |

| The contents of memory address 300 represent an unsigned binary integer.                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Write the denary value of the unsigned binary integer in memory address 300.                                                                |

| [1]                                                                                                                                         |

| An assembly language program needs to test if bit number $2$ in memory address $300$ is a $1$ .                                             |

| Complete the assembly language instruction to perform this test.                                                                            |

| #4                                                                                                                                          |

| An assembly language program needs to set bit numbers $4$ , $5$ , $6$ and $7$ to $0$ , but keep bits $0$ to $3$ with their existing values. |

| Write the assembly language instruction to perform this action.                                                                             |

|                                                                                                                                             |

| [2]                                                                                                                                         |

|                                                                                                                                             |

| 8 The Von Neumann model uses a series of registers. (a) Explain what is meant by the terr | · · |

|-------------------------------------------------------------------------------------------|-----|

|                                                                                           |     |

| ]                                                                                         |     |

| (b) (i) Explain the purpose of the Memory Data Register (MDR).                            |     |

|                                                                                           | 3   |

| (ii) Name two registers, other than the MDR, that are used in the fetch-execute cycle.    |     |

| Register 1                                                                                |     |

| Register 2[2                                                                              | 1   |

## 9608/11 Jun 17 Q4a

4 The following table shows part of the instruction set for a processor. The processor has one general purpose register, the Accumulator (ACC) and an Index Register (IX).

| Instruction           |                     |                     |                                                                                                                                                               |

|-----------------------|---------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Op code<br>(mnemonic) | Operand             | Op code<br>(binary) | Explanation                                                                                                                                                   |

| LDM                   | #n                  | 0000 0001           | Immediate addressing. Load the denary number n to ACC.                                                                                                        |

| LDD                   | <address></address> | 0000 0010           | Direct addressing. Load the contents of the location at the given address to ACC.                                                                             |

| LDI                   | <address></address> | 0000 0101           | Indirect addressing. At the given address is the address to be used. Load the contents of this second address to ACC.                                         |

| LDX                   | <address></address> | 0000 0110           | Indexed addressing. Form the address from <address> + the contents of the Index Register (IX). Copy the contents of this calculated address to ACC.</address> |

| LDR                   | #n                  | 0000 0111           | Immediate addressing. Load number n to IX.                                                                                                                    |

| STO                   | <address></address> | 0000 1111           | Store the contents of ACC at the given address.                                                                                                               |

The following diagram shows the contents of a section of main memory and the Index Register (IX).

(a) Show the contents of the Accumulator (ACC) after each instruction is executed.

| IX | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |  |

|----|---|---|---|---|---|---|---|---|--|

502

| (i)   |     | #500 | Address | Main<br>Memory<br>contents |

|-------|-----|------|---------|----------------------------|

|       | ACC | [1]  | 495     | 13                         |

| (ii)  | LDD | 500  | 496     | 86                         |

|       | ACC | [1]  | 497     | 92                         |

| (iii) | LDX | 500  | 498     | 486                        |

|       | ACC | [1]  | 499     | 489                        |

|       |     |      | 500     | 496                        |

| (iv)  | LDI | 500  | 501     | 497                        |

|       | ACC | [1]  | 502     | 499                        |

9608/13 Jun 18 Q3a, b

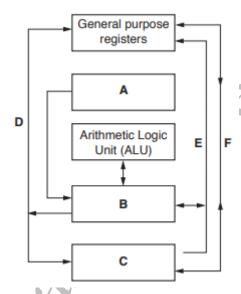

- 3 A computer is designed using the Von Neumann model.

- (a) Describe the role of the Arithmetic and Logic Unit (ALU) and Control Unit (CU) in the Von Neumann model.

.....

(b) Describe the role of the Status Register and Program Counter (PC).

Status Register

[4]

| [V. |

|-----|

| Γ.  |

9608/11 Nov 17 Q4

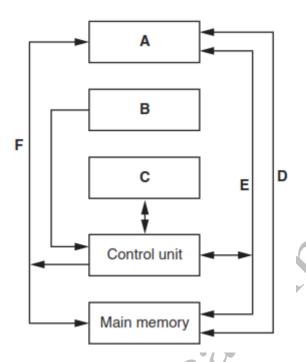

4 (a) The diagram shows the components and buses found inside a typical Personal Computer (PC).

Some components and buses only have labels  $\bf A$  to  $\bf F$  to identify them. For each label, choose the appropriate title from the following list. The title for label  $\bf D$  is already given.

- Control bus

- System clock

- Data bus

- Control unit

- Main memory

- Secondary storage

| Α             |   |

|---------------|---|

| В             |   |

| C             |   |

| D Address bus |   |

| E             |   |

| F             | [ |

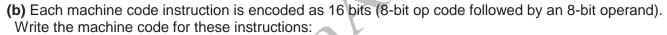

(b) The following table shows part of the instruction set for a processor. The processor has one general purpose register, the Accumulator (ACC), and an Index Register (IX).

| Op code (mnemonic) Operand |                     |                     |                                                                                                                                               |

|----------------------------|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                            |                     | Op code<br>(binary) | Explanation                                                                                                                                   |

| LDM                        | #n                  | 1100 0001           | Immediate addressing. Load number n to ACC.                                                                                                   |

| LDD                        | <address></address> | 1100 0010           | Direct addressing. Load the contents of the given address to ACC.                                                                             |

| LDV                        | #n                  | 1100 0011           | Relative addressing. Move to the address $n$ locations from the address of the current instruction. Load the contents of this address to ACC. |

| STO                        | <address></address> | 1100 0100           | Store the contents of ACC at the given address.                                                                                               |

| DEC                        |                     | 1100 0101           | Decrement the contents of ACC.                                                                                                                |

| OUTCH                      |                     | 1100 0111           | Output the character corresponding to the ASCII character code in ACC.                                                                        |

| JNE                        | <address></address> | 1110 0110           | Following a compare instruction, jump to <address> if the compare was False.</address>                                                        |

| JMP                        | <address></address> | 1110 0011           | (Unconditionally) jump to the given address.                                                                                                  |

| CMP                        | #n                  | 1110 0100           | Compare the contents of ACC with number n.                                                                                                    |

Complete the trace table for the following assembly language program.

| Label      | In    | struction  |

|------------|-------|------------|

| StartProg: | LDV   | #CountDown |

|            | CMP   | Num1       |

|            | JNE   | CarryOn    |

|            | JMP   | Finish     |

| CarryOn:   | OUTCH |            |

|            | LDD   | CountDown  |

|            | DEC   |            |

|            | STO   | CountDown  |

|            | JMP   | StartProg  |

| Finish:    | LDM   | #88        |

|            | OUTCH |            |

|            | END   |            |

| CountDown: |       | 15         |

|            |       | 32         |

|            |       | 51         |

|            |       | 67         |

| Num1:      |       | 32         |

| ASCII code table (selected codes only) |    |     |       |  |  |  |  |

|----------------------------------------|----|-----|-------|--|--|--|--|

| 3                                      | В  | С   | X     |  |  |  |  |

| 51                                     | 66 | 67  | 88    |  |  |  |  |

|                                        | 3  | 3 B | 3 B C |  |  |  |  |

#### Trace table:

| ACC | CountDown | OUTPUT |

|-----|-----------|--------|

|     | 15        |        |

| 67  |           | С      |

| 15  |           |        |

|     |           |        |

|     |           |        |

|     |           |        |

|     |           |        |

|     |           |        |

|     |           |        |

|     |           |        |

|     |           |        |

|     |           |        |

[5]

(c) The program given in part (b) is to be translated using a two-pass assembler.

The program has been copied here for you. The program now starts with a directive which tells the assembler to load the first instruction of the program to address 100.

#### Label

| assembler to I | oad the | first instructio | n of the program to add |

|----------------|---------|------------------|-------------------------|

| Label          |         |                  |                         |

|                | ORG     | #0100            |                         |

| StartProg:     | LDV     | #CountDown       | 17                      |

|                | CMP     | Num1             |                         |

|                | JNE     | CarryOn          |                         |

|                | JMP     | Finish           |                         |

| CarryOn:       | OUTCH   |                  | <b>Y</b>                |

|                | LDD     | CountDown        |                         |

|                | DEC     |                  |                         |

|                | STO     | CountDown        |                         |

|                | JMP     | StartProg        |                         |

| Finish:        | LDM     | #88              |                         |

|                | OUTCH   |                  |                         |

|                | END     |                  |                         |

| CountDown:     |         | 15               |                         |

|                |         | 32               |                         |

|                |         | 51               |                         |

|                |         | 67               |                         |

| Num1:          |         | 32               |                         |

|                |         |                  | e .                     |

On the first pass of the two-pass process, the assembler adds entries to a symbol table.

The following symbol table shows the first eleven entries, part way through the first pass.

The circular labels show the order in which the assembler made the entries to the symbol table.

#### Symbol table

| Symbolic address |   | Absolute address |  |  |

|------------------|---|------------------|--|--|

| StartProg        | 1 | 100 2            |  |  |

| CountDown        | 3 | UNKNOWN 4        |  |  |

| Num1             | 5 | UNKNOWN 6        |  |  |

| CarryOn          | 7 | UNKNOWN 8 104 11 |  |  |

| Finish           | 9 | UNKNOWN (10)     |  |  |

| Explain how the assembler made these entries to the symbol table.                              |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

|                                                                                                |

| $\alpha^{\gamma}$                                                                              |

|                                                                                                |

| [3]                                                                                            |

| (d) The assembler software must then complete the second pass building up the executable file. |

| (i) Name the second table needed when the assembler software carries out the second pass.      |

| [1]                                                                                            |

| The following shows two of the program instructions in machine code.                           |

|             | Machine code |             |  |  |

|-------------|--------------|-------------|--|--|

| Instruction | Binary       | Hexadecimal |  |  |

| OUTCH       | 1100 0111    | C7          |  |  |

| JNE CarryOn | Α            | В           |  |  |

Each of the numbers  $\bf A$  and  $\bf B$  represents the complete instruction in two bytes, one byte for the op code and one byte for the operand.

| (ii) Use the following instruction set to write the numbers for A and B. |

|--------------------------------------------------------------------------|

| A (binary)                                                               |

| <b>B</b> (hexadecimal)[3]                                                |

| Instru                | ıction              |                     |                                                                                                                                               |

|-----------------------|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Op code<br>(mnemonic) | Operand             | Op code<br>(binary) | Explanation                                                                                                                                   |

| LDM                   | #n                  | 1100 0001           | Immediate addressing. Load number n to ACC.                                                                                                   |

| LDD                   | <address></address> | 1100 0010           | Direct addressing. Load the contents of the given address to ACC.                                                                             |

| LDV                   | #n                  | 1100 0011           | Relative addressing. Move to the address $n$ locations from the address of the current instruction. Load the contents of this address to ACC. |

| STO                   | <address></address> | 1100 0100           | Store the contents of ACC at the given address.                                                                                               |

| DEC                   |                     | 1100 0101           | Decrement the contents of ACC.                                                                                                                |

| OUTCH                 |                     | 1100 0111           | Output the character corresponding to the ASCII character code in ACC.                                                                        |

| JNE                   | <address></address> | 1110 0110           | Following a compare instruction, jump to <address> if the compare was False.</address>                                                        |

| JMP                   | <address></address> | 1110 0011           | (Unconditionally) jump to the given address.                                                                                                  |

| CMP                   | #n                  | 1110 0100           | Compare the contents of ACC with number n.                                                                                                    |

#### 9608/11 Nov 18 Q4a, b, d

4 The table shows assembly language instructions for a processor which has one general purpose register, the Accumulator (ACC) and an index register (IX).

| Inst    | truction              | Explanation                                                                                                                                              |  |  |  |

|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Op code | Operand               | Explanation                                                                                                                                              |  |  |  |

| LDD     | <address></address>   | Direct addressing. Load the contents of the location at the given address to ACC.                                                                        |  |  |  |

| LDX     | <address></address>   | Indexed addressing. Form the address from <address> + the contents of the Index Register. Copy the contents of this calculated address to ACC.</address> |  |  |  |

| LDR     | #n                    | Immediate addressing. Load the number n to IX.                                                                                                           |  |  |  |

| STO     | <address></address>   | Store contents of ACC at the given address.                                                                                                              |  |  |  |

| ADD     | <address></address>   | Add the contents of the given address to ACC.                                                                                                            |  |  |  |

| INC     | <register></register> | Add 1 to the contents of the register (ACC or IX).                                                                                                       |  |  |  |

| DEC     | <register></register> | Subtract 1 from the contents of the register (ACC or IX).                                                                                                |  |  |  |

| CMP     | <address></address>   | Compare contents of ACC with contents of <address>.</address>                                                                                            |  |  |  |

| JPE     | <address></address>   | Following a compare instruction, jump to <address> if the compare was True.</address>                                                                    |  |  |  |

| JPN     | <address></address>   | Following a compare instruction, jump to <address> if the compare was False.</address>                                                                   |  |  |  |

| JMP     | <address></address>   | Jump to the given address.                                                                                                                               |  |  |  |

| OUT     |                       | Output to the screen the character whose ASCII value is stored in ACC.                                                                                   |  |  |  |

| END     |                       | Return control to the operating system.                                                                                                                  |  |  |  |

| (a) (i) State what is m<br>Direct addressing     |           | •         |          | •        |          |          |                 |         |              |          |              |

|--------------------------------------------------|-----------|-----------|----------|----------|----------|----------|-----------------|---------|--------------|----------|--------------|

| Indirect addressing .                            |           |           |          |          |          |          |                 |         |              |          |              |

| (ii) Explain how the                             |           |           |          |          |          |          |                 |         |              | occina   |              |

| Direct addressing                                |           |           |          |          | •        |          |                 |         |              | #55IIIg. |              |

|                                                  |           |           |          |          |          |          |                 |         |              |          |              |

| Indirect addressing .                            |           |           |          |          |          |          |                 |         |              | <b>3</b> |              |

|                                                  |           |           |          |          |          |          |                 |         | [2]          |          |              |

|                                                  |           |           |          |          |          |          |                 |         | 1.           |          |              |

| <b>(b)</b> The assembly lan absolute addressing. | iguage    | instructi | ons in t | he follo | wing ta  | ble use  | either          | symbol  | ic addressin | g or     |              |

| Tick (✓) <b>one</b> box in                       | each ro   | ow to inc | licate w | hether   | the inst | ruction  | uses <u>s</u> y | ymbolic | or absolute  | addres   | sing.        |

|                                                  | Instr     | uction    | !        | Symbol   | ic       | A        | bsolute         | 9       |              |          |              |

|                                                  | ADD 9     | 0         |          |          |          |          |                 |         |              |          |              |

|                                                  | CMP f     | ound      |          |          |          |          |                 |         |              |          |              |

|                                                  | STO 2     | 0         |          |          |          |          |                 |         |              |          |              |

| (c) The curre                                    | ent conte | ents of a | general  | purpose  | register | (X) are: |                 |         |              | [2]      |              |

|                                                  |           |           |          |          |          |          |                 |         | 7            |          |              |

| Х                                                | 1         | 0         | 1        | 1        | 1        | 0        | 1               | 0       |              |          |              |

| (i) The contents of >                            | K repres  | sent an i | unsigne  | ed binar | y intege | er.      |                 |         |              |          |              |

| Convert the value in                             | n X into  | denary    |          |          |          |          |                 |         |              |          |              |

|                                                  | \X        |           |          |          |          |          |                 |         | [1]          |          | <u>Ch</u> #1 |

| (ii) The contents of                             |           |           | _        | ed bina  | ry integ | er.      |                 |         |              |          |              |

| Convert the value i                              |           |           |          |          |          |          |                 |         | [4]          |          |              |

| (iii) The contents of                            |           |           |          |          |          |          |                 |         | [1]          |          |              |

| Convert the value in                             | •         |           |          |          |          | <i>,</i> | J ~ · ·         |         |              |          |              |

|                                                  |           |           |          |          |          |          |                 |         | [1 <u>]</u>  |          |              |

(d) The current contents of the main memory, Index Register (IX) and selected values from the ASCII character set are provided with a copy of the instruction set.

# Address Instruction

| ress | Instruction |

|------|-------------|

| 70   | LDX 200     |

| 71   | OUT         |

| 72   | STO 203     |

| 73   | LDD 204     |

| 74   | INC ACC     |

| 75   | STO 204     |

| 76   | INC IX      |

| 77   | LDX 200     |

| 78   | CMP 203     |

| 79   | JPN 81      |

| 80   | OUT         |

| 81   | LDD 204     |

| 82   | CMP 205     |

| 83   | JPN 74      |

| 84   | END         |

|      |             |

| 200  | 130         |

| 201  | 133         |

| 202  | 130         |

| 203  | 0           |

| 204  | 0           |

| 205  | 2           |

|    | _ |

|----|---|

| IX | 0 |

|    |   |

#### ASCII code table (selected codes only)

| ASCII code | Character |

|------------|-----------|

| 127        | ?         |

| 128        | !         |

| 129        | 44        |

| 130        | *         |

| 131        | \$        |

| 132        | &         |

| 133        | %         |

| 134        | 1         |

#### Instruction set

| Instruction |                       |                                                                                                                                                          |

|-------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Op<br>code  | Operand               | Explanation                                                                                                                                              |

| LDD         | <address></address>   | Direct addressing. Load the contents of the location at the given address to ACC.                                                                        |

| LDX         | <address></address>   | Indexed addressing. Form the address from <address> + the contents of the Index Register. Copy the contents of this calculated address to ACC.</address> |

| LDR         | #n                    | Immediate addressing. Load the number n to IX.                                                                                                           |

| STO         | <address></address>   | Store contents of ACC at the given address.                                                                                                              |

| ADD         | <address></address>   | Add the contents of the given address to ACC.                                                                                                            |

| INC         | <register></register> | Add 1 to the contents of the register (ACC or IX).                                                                                                       |

| DEC         | <register></register> | Subtract 1 from the contents of the register (ACC or IX).                                                                                                |

| CMP         | <address></address>   | Compare contents of ACC with contents of <address>.</address>                                                                                            |

| JPE         | <address></address>   | Following a compare instruction, jump to <address> if the compare was True.</address>                                                                    |

| JPN         | <address></address>   | Following a compare instruction, jump to <address> if the compare was False.</address>                                                                   |

| JMP         | <address></address>   | Jump to the given address.                                                                                                                               |

| OUT         |                       | Output to the screen the character whose ASCII value is stored in ACC.                                                                                   |

| END         |                       | Return control to the operating system.                                                                                                                  |

Complete the trace table for the given assembly language program.

| Instruction | ACC | Memory address |     |     |     |     |     |    | ОИТРИТ  |

|-------------|-----|----------------|-----|-----|-----|-----|-----|----|---------|

| address     |     | 200            | 201 | 202 | 203 | 204 | 205 | IX | 0011 01 |

| 70          | 130 | 130            | 133 | 130 | 0   | 0   | 2   | 0  |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

|             |     |                |     |     |     |     |     |    |         |

[8]

9608/12 Nov 17 Q4

**4** The following diagram shows the components and buses found inside a typical personal computer (PC).

- (a) Some components and buses only have labels **A** to **F** to identify them. For each label, choose the appropriate title from the following list. The title for label **D** is already given.

- Control bus

- Address bus

- Arithmetic Logic Unit (ALU)

- General purpose registers

- Secondary storage

- System clock

| Α    |                                                                                       |      |

|------|---------------------------------------------------------------------------------------|------|

| В    | • / '                                                                                 |      |

| C    |                                                                                       |      |

| D I  | Data bus                                                                              |      |

| F    |                                                                                       | .[5] |

| (b)  | Clock speed is a factor that affects the performance of a PC. Explain this statement. |      |

| •••• |                                                                                       |      |

| •••• |                                                                                       |      |

#### COMPILED BY S.M.RAZA

| (c) An assembly language program can contain both <b>macros</b> and <b>directives</b> .  (i) Explain what is meant by these terms. |  |

|------------------------------------------------------------------------------------------------------------------------------------|--|

| Macro                                                                                                                              |  |

|                                                                                                                                    |  |

| Directive                                                                                                                          |  |

| (ii) Give an example of the use of a directive.                                                                                    |  |

| (d) The following table shows part of the instruction set for a processor. The processor has one                                   |  |

| (u) The following table shows part of the instruction set for a processor. The processor has one                                   |  |

general purpose register, the Accumulator (ACC), and an Index Register (IX).

| Instru                | ıction              |                                                                                                                                             |

|-----------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Op code<br>(mnemonic) | Operand             | Explanation                                                                                                                                 |

| LDD                   | <address></address> | Direct addressing. Load the contents of the given address to ACC.                                                                           |

| LDV                   | #n                  | Relative addressing. Move to the address n locations from the address of the current instruction. Load the contents of this address to ACC. |

| STO                   | <address></address> | Store the contents of ACC at the given address.                                                                                             |

| INC                   |                     | Increment the contents of ACC.                                                                                                              |

| OUTCH                 |                     | Output the character corresponding to the ASCII character code in ACC.                                                                      |

| JPE                   | <address></address> | Following a compare instruction, jump to <address> if the compare was True.</address>                                                       |

| JMP                   | <address></address> | Jump to the given address.                                                                                                                  |

| CMP                   | #n                  | Compare the contents of ACC with number n.                                                                                                  |

Complete the trace table for the following assembly language program.

| Label      | Instruction |           |  |  |  |  |

|------------|-------------|-----------|--|--|--|--|

| StartProg: | LDV         | #Offset   |  |  |  |  |

|            | CMP         | Value     |  |  |  |  |

|            | JPE         | EndProg   |  |  |  |  |

|            | OUTCE       | I         |  |  |  |  |

|            | LDD         | Offset    |  |  |  |  |

|            | INC         |           |  |  |  |  |

|            | STO         | Offset    |  |  |  |  |

|            | JMP         | StartProg |  |  |  |  |

| EndProg:   | END         |           |  |  |  |  |

| Offset:    |             | 10        |  |  |  |  |

|            |             | 50        |  |  |  |  |

|            |             | 65        |  |  |  |  |

|            |             | 89        |  |  |  |  |

|            |             | 32        |  |  |  |  |

| Value:     |             | 32        |  |  |  |  |

| ASCII code table (selected codes only) |    |    |    |    |  |  |  |  |

|----------------------------------------|----|----|----|----|--|--|--|--|

| <space> 2 A B Y</space>                |    |    |    |    |  |  |  |  |

| 32                                     | 50 | 65 | 66 | 89 |  |  |  |  |

#### Trace table:

| ACC | Offset | ОИТРИТ |

|-----|--------|--------|

|     | 10     |        |

| 50  |        | 2      |

| 10  |        |        |

|     |        |        |

|     |        |        |

|     |        |        |

|     |        |        |

|     |        |        |

|     |        |        |

|     |        |        |

|     |        |        |

|     |        |        |

[5]

(e) The program given in **part** (d) is to be translated using a two-pass assembler. The program has been copied here for you.

| Label      | Instruction |           |  |  |  |  |

|------------|-------------|-----------|--|--|--|--|

| StartProg: | LDV         | #Offset   |  |  |  |  |

|            | CMP         | Value     |  |  |  |  |

|            | JPE         | EndProg   |  |  |  |  |

|            | OUTC        | Н         |  |  |  |  |

|            | LDD         | Offset    |  |  |  |  |

|            | INC         |           |  |  |  |  |

|            | STO         | Offset    |  |  |  |  |

|            | JMP         | StartProg |  |  |  |  |

| EndProg:   | END         |           |  |  |  |  |

| Offset:    |             | 10        |  |  |  |  |

|            |             | 50        |  |  |  |  |

|            |             | 65        |  |  |  |  |

|            |             | 89        |  |  |  |  |

|            |             | 32        |  |  |  |  |

| Value:     |             | 32        |  |  |  |  |

On the first pass, the assembly process adds entries to a symbol table.

The following symbol table shows the first five entries, part way through the first pass.

The circular labels show the order in which the assembler made the entries to the symbol table.

Complete the symbol table. Use circular labels to show the order in which the assembler makes the entries.

Symbol table

| Symbolic address | Relative address |  |  |  |  |

|------------------|------------------|--|--|--|--|

| StartProg 1      | 0 2              |  |  |  |  |

| Offset 3         | UNKNOWN 4        |  |  |  |  |

| Value 5          |                  |  |  |  |  |

|                  |                  |  |  |  |  |

9608/12 Nov 18 Q3

**3** The following table shows assembly language instructions for a processor which has one general purpose register, the Accumulator (ACC) and an Index Register (IX).

| Instruction |                       | Evalenation                                                                                                                                              |  |  |  |  |  |

|-------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Op code     | Operand               | Explanation                                                                                                                                              |  |  |  |  |  |

| LDD         | <address></address>   | Direct addressing. Load the contents of the location at the given address to ACC.                                                                        |  |  |  |  |  |

| LDX         | <address></address>   | Indexed addressing. Form the address from <address> + the contents of the Index Register. Copy the contents of this calculated address to ACC.</address> |  |  |  |  |  |

| LDR         | #n                    | Immediate addressing. Load the number n to IX.                                                                                                           |  |  |  |  |  |

| STO         | <address></address>   | Store contents of ACC at the given address.                                                                                                              |  |  |  |  |  |

| ADD         | <address></address>   | Add the contents of the given address to ACC.                                                                                                            |  |  |  |  |  |

| INC         | <register></register> | Add 1 to the contents of the register (ACC or IX).                                                                                                       |  |  |  |  |  |

| DEC         | <register></register> | Subtract 1 from the contents of the register (ACC or IX).                                                                                                |  |  |  |  |  |

| CMP         | <address></address>   | Compare contents of ACC with contents of <address>.</address>                                                                                            |  |  |  |  |  |

| JPE         | <address></address>   | Following compare instruction, jump to <address> if the compare was True.</address>                                                                      |  |  |  |  |  |

| JPN         | <address></address>   | Following compare instruction, jump to <address> if the compare was False.</address>                                                                     |  |  |  |  |  |

| JMP         | <address></address>   | Jump to the given address.                                                                                                                               |  |  |  |  |  |

| OUT         |                       | Output to the screen the character whose ASCII value is stored in ACC.                                                                                   |  |  |  |  |  |

| END         |                       | Return control to the operating system.                                                                                                                  |  |  |  |  |  |

| (a) (i) State what is meant by a |        |         |        | _              | -              | / )    |       |        | _           |

|----------------------------------|--------|---------|--------|----------------|----------------|--------|-------|--------|-------------|

| Absolute addressing              |        |         |        |                |                |        |       |        |             |

|                                  |        |         |        |                |                |        |       |        |             |

| Symbolic addressing              |        |         |        | \              |                |        |       |        |             |

|                                  |        |         |        | 7              |                |        |       |        | [2]         |

| (ii) Give an example of an AI    | D ins  | tructio | n usin | g both         | n abso         | lute a | ddres | sing a | nd symbolic |

| addressing.                      |        |         |        |                |                |        |       |        |             |

| Absolute addressing              |        |         |        |                |                |        |       |        |             |

| Symbolic addressing              |        |         |        |                |                |        |       |        |             |

| Cymbolic addressing              |        |         |        |                |                |        |       |        | [4]         |

| (b) (i) State what is meant by   | index  | ed ad   | dress  | i <b>ng</b> ar | nd <b>im</b> ı | nedia  | te ad | dress  | ing.        |

| Indexed addressing               |        |         |        |                |                |        |       |        |             |

|                                  |        |         |        |                |                |        |       |        |             |

| Immediate addressing             |        |         |        |                |                |        |       |        |             |

|                                  |        |         |        |                |                |        |       |        |             |

| (ii) Give an example of an ins   |        |         |        |                |                |        |       |        | [2]         |

|                                  |        |         |        |                |                |        |       |        |             |

| Indexed addressing               |        |         |        |                |                |        |       |        |             |

| Immediate addressing             |        |         |        |                |                |        |       |        | [2]         |

| (c) The current contents of a g  | jenera | al purp | ose re | egister        | · (X) a        | re:    |       |        |             |

|                                  |        |         |        |                |                |        |       |        | 1           |

| X                                | 1      | 1       | 0      | 0              | 0              | 0      | 0     | 1      |             |

|                                  |        |         |        |                |                |        |       |        |             |

| (i) The contents of X represent an unsigned binary integer.          |     |

|----------------------------------------------------------------------|-----|

| Convert the value in X into denary.                                  |     |

|                                                                      | [1] |

| (ii) The contents of X represent an unsigned binary integer.         |     |

| Convert the value in X into hexadecimal.                             |     |

|                                                                      | [1] |

| (iii) The contents of X represent a two's complement binary integer. |     |

| Convert the value in X into denary.                                  | A   |

|                                                                      | [1] |

# (d) The current contents of the main memory, Index Register (IX) and selected values from the ASCII character set are:

| Address | Instruction |

|---------|-------------|

| 40      | LDD 100     |

| 41      | CMP 104     |

| 42      | JPE 54      |

| 43      | LDX 100     |

| 44      | CMP 105     |

| 45      | JPN 47      |

| 46      | OUT         |

| 47      | LDD 100     |

| 48      | DEC ACC     |

| 49      | STO 100     |

| 50      | INC IX      |

| 51      | JMP 41      |

| 52      |             |

| 53      |             |

| 54      | END         |

|         | )           |

|         |             |

| 100     | 2           |

| 101     | 302         |

| 102     | 303         |

| 103     | 303         |

| 104     | 0           |

| IX | 1 |

|----|---|

|    |   |

This is a copy of the instruction set.

# ASCII code table (selected codes only)

| ASCII code | Character |

|------------|-----------|

| 300        | /         |

| 301        | *         |

| 302        | -         |

| 303        | +         |

| 304        | ۸         |

| 305        | =         |

| Instruction |                       | Evalenation                                                                                                                                              |  |  |  |  |

|-------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Op code     | Operand               | Explanation                                                                                                                                              |  |  |  |  |

| LDD         | <address></address>   | Direct addressing. Load the contents of the location at the given address to ACC.                                                                        |  |  |  |  |

| LDX         | <address></address>   | Indexed addressing. Form the address from <address> + the contents of the Index Register. Copy the contents of this calculated address to ACC.</address> |  |  |  |  |

| LDR         | #n                    | Immediate addressing. Load the number n to IX.                                                                                                           |  |  |  |  |

| STO         | <address></address>   | Store contents of ACC at the given address.                                                                                                              |  |  |  |  |

| ADD         | <address></address>   | Add the contents of the given address to ACC.                                                                                                            |  |  |  |  |

| INC         | <register></register> | Add 1 to the contents of the register (ACC or IX).                                                                                                       |  |  |  |  |

| DEC         | <register></register> | Subtract 1 from the contents of the register (ACC or IX).                                                                                                |  |  |  |  |

| CMP         | <address></address>   | Compare contents of ACC with contents of <address>.</address>                                                                                            |  |  |  |  |

| JPE         | <address></address>   | Following a compare instruction, jump to <address> if the compare was True.</address>                                                                    |  |  |  |  |

| JPN         | <address></address>   | Following a compare instruction, jump to <address> if the compare was False.</address>                                                                   |  |  |  |  |

| JMP         | <address></address>   | Jump to the given address.                                                                                                                               |  |  |  |  |

| OUT         |                       | Output to the screen the character whose ASCII value is stored in ACC.                                                                                   |  |  |  |  |

| END         |                       | Return control to the operating system.                                                                                                                  |  |  |  |  |

Complete the trace table for the given assembly language program.

| Instruction address | ACC | Memory address |     |     |     | Memory ad |     |    | IX     | ОИТРИТ |

|---------------------|-----|----------------|-----|-----|-----|-----------|-----|----|--------|--------|

|                     |     | 100            | 101 | 102 | 103 | 104       | 105 | 1. | OUIPUI |        |

|                     |     | 2              | 302 | 303 | 303 | 0         | 303 | 1  |        |        |

| 40                  |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

|                     |     |                |     |     |     |           |     |    |        |        |

[7]

# 9608/12 Nov 18 Q4

**4** A student has written the steps of the fetch stage of the fetch-execute (FE) cycle in register transfer notation. The student has made some errors.

| Line | 1 | MDR | $\leftarrow$ | [PC]   |

|------|---|-----|--------------|--------|

| Line | 2 | PC  | $\leftarrow$ | PC + 1 |

| Line | 3 | MDR | $\leftarrow$ | [MAR]  |

| Line | 4 | CIR | $\leftarrow$ | PC     |

(a) Identify the line numbers of **three** errors that the student has made. Write the correct notation for each error.

| Correct notation |

|------------------|

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |